Le CEA-Leti et Intel coopèrent pour étendre la loi de Moore au-delà de 2030

Le centre de recherche et le fabricant de puces travaillent sur une nouvelle génération de matériaux semiconducteurs monocouches très prometteurs, car susceptibles de faire vivre encore la loi de Moore pendant de longues années.

A l’heure où la loi de Moore semble sur le point d’atteindre ses limites, de nombreux acteurs de la microélectronique travaillent d’arrache-pied sur des projets de R&D visant à redonner un nouveau souffle à la règle emblématique de la microélectronique pour la faire vivre encore de nombreuses années.

C’est l’objectif du programme de recherche pluriannuel conjoint que viennent d’annoncer le CEA-Leti et Intel. Déjà partenaires sur des projets tels que le packaging 3D , le géant américain des puces électroniques et le centre de R&D grenoblois vont développer, dans cadre de ce nouveau projet, une technologie de transfert de couche de dichalcogénures de métaux de transition bidimensionnels (2D TMD) sur des tranches de 300 mm, dans le but d’étendre la loi de Moore au-delà de 2030.

© CEA-leti

A l’instar du graphène, les dichalcogénures de métaux de transition (TMD) sont des matériaux semiconducteurs monocouches – donc bidimensionnels (2D) – aux propriétés très prometteuses pour les applications de microélectronique.

« Alors que nous poussons sans relâche la loi de Moore, le matériau 2D TMD est une option prometteuse pour repousser les limites de la mise à l’échelle des transistors à l’avenir, assure Robert Chau, directeur d’Intel Europe Research. Ce programme de recherche se concentre sur le développement d’une technologie viable basée sur des substrats de 300 mm. »

Les semi-conducteurs monocouches, tels que les 2D TMD à base de molybdène et de tungstène, sont des candidats prometteurs pour étendre la loi de Moore et assurer une mise à l’échelle ultime des transistors Mosfet, car les FET 2D fournissent une épaisseur de canal de transistor native inférieure au nanomètre. Ils peuvent ainsi mener au développement de plateformes hautes performances et à faible consommation en raison de leur bon transfert de charges et de leur mobilité, même pour des couches atomiquement minces. A cela s’ajoute un contrôle électrostatique amélioré – et donc de faibles courants à l’état bloqué – lié, notamment, à leur bande interdite d’énergie modérée.

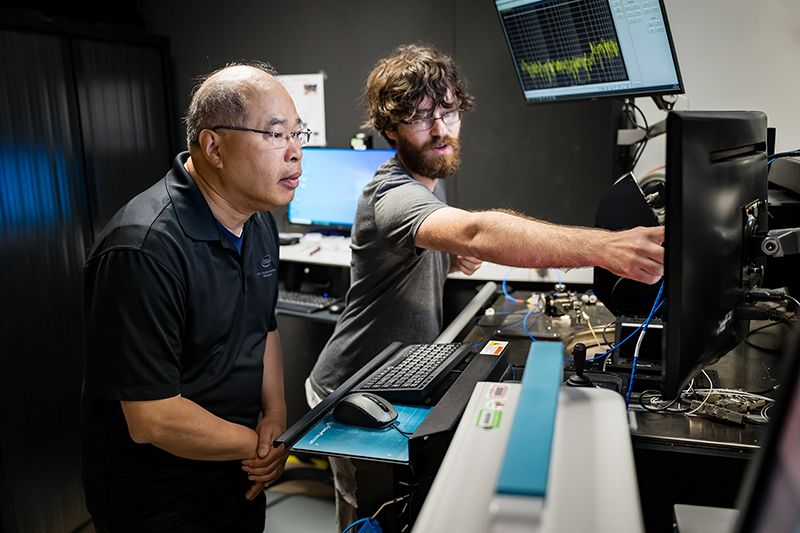

Sébastien Dauvé, Pdg du CEA-Leti (à gauche), et Robert Chau, directeur d’Intel Europe Research – © CEA-Leti

Ces caractéristiques positionnent les dispositifs à nanofeuilles empilées 2D-FET comme une solution prometteuse pour la mise à l’échelle des transistors au-delà de 2030, mais cela nécessitera une croissance de canaux 2D de haute qualité sur des substrats de 300 mm ainsi qu’un transfert adapté sur un autre substrat pour le procédé d’intégration des transistors, le tout dans le cadre d’un process fiable et robuste.

Pour ce faire, Intel apporte des décennies d’expertise en R&D et en fabrication tandis que le CEA-Leti fournit son expérience dans le domaine des couches de liaison et de transfert et de la caractérisation à grande échelle.

Pour Sébastien Dauvé, Pdg du CEA-Leti, la capacité de transfert sur des tranches de 300 mm sera la clé de cette intégration. « En raison de leur température de croissance élevée dépassant 700°C et de leur croissance de haute qualité sur les substrats, il est difficile d’empiler des matériaux 2D à la manière des couches minces habituelles. Le transfert est donc le moyen le plus prometteur pour les intégrer dans les futurs dispositifs, et les atouts du CEA-Leti dans ce contexte sont son expertise et son savoir-faire dans le développement et la caractérisation du transfert », conclut le dirigeant du centre de recherche.