La vente de Toshiba Memory à un consortium japonais est remise en cause

Ultime (?) rebondissement dans la saga de la vente de l’activité mémoires de Toshiba. Le groupe japonais aurait finalement décidé de ne pas fermer la porte aux offres de reprise de Western Digital et de Foxconn, annonce ce matin la presse nippone.

On croyait le dossier bouclé : le 21 juin, Toshiba annonçait officiellement le choix du repreneur : un consortium d’investisseurs composé du fonds japonais public-privé INCJ (Innovation Network Corp. of Japan) allié au fond d’investissement Bain Capital et à la Development Bank of Japan. Annoncée pour le 28 juin, la signature de l’accord définitif avait été repoussée. En cause, l’association indirecte du fabricant de mémoires coréen SK Hynix dans le consortium d’investisseurs qui doit racheter Toshiba Memory. Le rôle d’Hynix n’a jamais été précisé officiellement. Mais selon le Nikkei, il semble que les prétentions du Coréen font craindre que les autorités antitrust puissent ne pas délivrer les autorisations nécessaires à la transaction. Sans compter le risque d’une fuite de la technologie de Toshiba hors du Japon.

Devant ces incertitudes, Toshiba aurait annoncé aux banques sa décision de rouvrir les négociations avec Western Digital (son partenaire actuel dans les flash) et aussi avec le Taïwanais Foxconn. D’autant que Western Digital aurait soumis une offre associant le fonds d’investissement américain KKR, mais aussi INCJ (Innovation Network Corp. of Japan) et la Development Bank of Japan.

Toshiba aurait ainsi l’intention de convoquer une assemblée extraordinaire des actionnaires pour octobre prochain. Après l’obtention des autorisations réglementaires dans divers pays, la date effective de la cession est toujours prévue d’ici mars 2018.

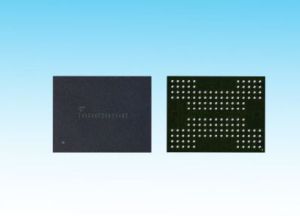

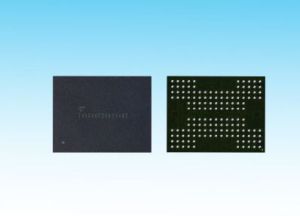

Première mémoire flash 3D dotée de la technologie TSV

Pendant ce temps, l’activité se poursuit. Ainsi, Toshiba annonce le développement de la première mémoire flash tridimensionnelle (3D) BiCS FLASH utilisant la technologie Through Silicon Via (TSV) avec la technologie de 3 bits par cellule (cellule triple niveau, triple-level cell, TLC). Les prototypes à des fins de développement ont commencé à être livrés en juin et les échantillons de produits devraient être disponibles durant la seconde moitié de 2017.

Pendant ce temps, l’activité se poursuit. Ainsi, Toshiba annonce le développement de la première mémoire flash tridimensionnelle (3D) BiCS FLASH utilisant la technologie Through Silicon Via (TSV) avec la technologie de 3 bits par cellule (cellule triple niveau, triple-level cell, TLC). Les prototypes à des fins de développement ont commencé à être livrés en juin et les échantillons de produits devraient être disponibles durant la seconde moitié de 2017.

Les dispositifs fabriqués à l’aide de la technologie TSV comportent des vias et des électrodes verticales qui traversent les microcircuits en silicium pour assurer des connexions, une architecture qui réalise une entrée et une sortie de données à grande vitesse, tout en réduisant la consommation électrique.

En combinant un processus flash 3D à 48 couches et la technologie TSV, Toshiba Memory a réussi à augmenter la bande passante de programmation du produit tout en réduisant la consommation énergétique. L’efficacité énergétique d’un seul boîtier est environ deux fois celle de la mémoire BiCS FLASH de même génération fabriquée à l’aide de la technologie de câblage filaire. La TSV BiCS FLASH permet également d’obtenir un dispositif de 1 téraoctet (To) doté d’une architecture empilée de 16 couches dans un seul boîtier.