La France organise la semaine prochaine la deuxième semaine RISC-V

Du 30 mars au 1er avril 2021, l’IRT Nanoelec, CEA Tech, Inria, et l’OpenHW Group organisent la deuxième semaine RISC-V, un évènement en ligne et en présentiel à Rennes, Grenoble & Paris-Saclay. La sessions précédente (fin 2019) avait rassemblée 120 participants. Cette fois, 280 personnes du monde entier sont inscrites pour ce colloque.

Au programme de la deuxième semaine RISC-V : cours, conférences, sessions thématiques et tables rondes avec des intervenants des organisations suivantes : ETH Zürich, UNSW, Google, Thales, Université de Nantes, Bluespec, Inc, Semidynamics Technology Services, Centre national de la recherche scientifique, Carnegie Mellon University, Huawei, Grenoble INP Esisar, STMicroelectronics, Université Grenoble Alpes, Université Paris-Saclay…

Au programme de la deuxième semaine RISC-V : cours, conférences, sessions thématiques et tables rondes avec des intervenants des organisations suivantes : ETH Zürich, UNSW, Google, Thales, Université de Nantes, Bluespec, Inc, Semidynamics Technology Services, Centre national de la recherche scientifique, Carnegie Mellon University, Huawei, Grenoble INP Esisar, STMicroelectronics, Université Grenoble Alpes, Université Paris-Saclay…

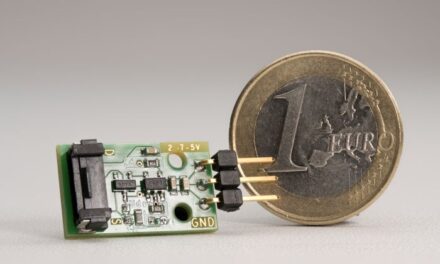

RISC-V est une architecture de jeu d’instruction (ISA : Instruction Set Architecture) gratuit et ouvert qui ouvre de nouveaux horizons dans l’innovation sur les processeurs. Les concepteurs de matériel et de logiciel, qu’ils soient industriels, universitaires ou contributeurs individuels, collaborent au développement des cœurs RISC-V, de la propriété intellectuelle associée, des outils et des logiciels. La communauté rassemblée autour de RISC-V explore de nouvelles possibilités en matière de logiciel et de matériel, avec des solutions gratuites et extensibles sur l’architecture.