Bloc d’IP de processeur dédié aux applications d’intelligence artificielle | Cadence

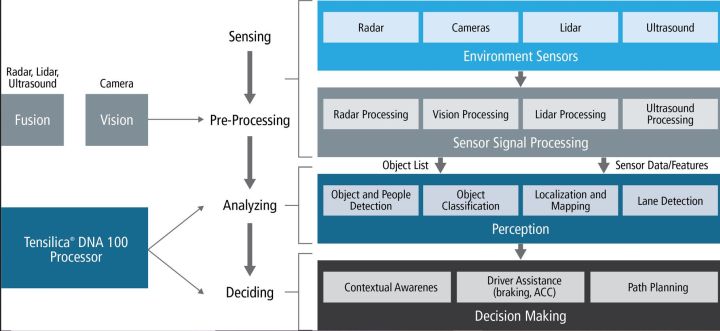

Cadence Design Systems annonce sous la référence Cadence Tensilica DNA 100 Processor IP, le premier processeur d’intelligence artificielle accélérateur de réseaux de neurones profonds (DNA — Deep Neural-network Accelerator) conjuguant à la fois des performances et un rendement énergétique élevés dans une large plage de puissance de calcul comprise entre 0,5 et plusieurs centaines de TeraMAC (TMAC).

Vendu sous la forme d’un bloc d’IP, le processeur DNA 100 convient à l’exécution de tâches d’inférence dans les réseaux de neurones intégrés à une large palette d’applications comme les véhicules autonomes, l’assistance à la conduite automobile (ADAS), la surveillance, la robotique, les drones, la réalité augmentée (AR) et la réalité virtuelle (VR), les smartphones, les maisons connectées ou encore l’Internet des objets (IoT). Selon Cadence, ce processeur allie des performances jusqu’à 4,7 fois supérieures et un rendement énergétique par Watt jusqu’à 2,3 fois supérieur à d’autres solutions affichant des dimensions MAC (multiplicateur-accumulateur) similaires.

Vendu sous la forme d’un bloc d’IP, le processeur DNA 100 convient à l’exécution de tâches d’inférence dans les réseaux de neurones intégrés à une large palette d’applications comme les véhicules autonomes, l’assistance à la conduite automobile (ADAS), la surveillance, la robotique, les drones, la réalité augmentée (AR) et la réalité virtuelle (VR), les smartphones, les maisons connectées ou encore l’Internet des objets (IoT). Selon Cadence, ce processeur allie des performances jusqu’à 4,7 fois supérieures et un rendement énergétique par Watt jusqu’à 2,3 fois supérieur à d’autres solutions affichant des dimensions MAC (multiplicateur-accumulateur) similaires.

Les réseaux neuronaux se caractérisent par la rareté inhérente de leurs activations et de leur poids causant, dans les processeurs ordinaires, une consommation inutile des chargements et les multiplications de zéros par les multiplicateurs-accumulateurs MAC. Le moteur de calcul matériel spécialisé du processeur DNA 100 élimine ces deux tâches, réduisant les besoins en calcul et améliorant l’efficacité énergétique. L’apprentissage des réseaux neuronaux permet d’augmenter la parcimonie des réseaux et d’obtenir le maximum de performances à l’aide du moteur de calcul du processeur DNA 100. Cela permet au processeur DNA 100 de maximiser le débit avec un réseau de dimensions inférieures, comme en témoigne sa capacité à atteindre 2 550 trames par seconde (fps) pour une consommation de 3,4 TMAC/watt (en technologie de 16 nm) en performances d’inférence estimées sur un réseau neuronal ResNet 50 pour une configuration MAC de 4 K.

Le processeur DNA 100 est livré avec une plateforme logicielle d’intelligence artificielle complète. Sa compatibilité avec la dernière version du compilateur de réseaux de neurones Tensilica autorise la prise en charge d‘environnement d’intelligence artificielle avancés, tels que Caffe, TensorFlow et TensorFlow Lite, ainsi que d’un large éventail de réseaux neuronaux, dont les réseaux convolutifs et récurrents. Fort de ces avantages, le processeur DNA 100 constitue une solution de choix pour l’exécution intégrée des tâches d’inférence dans les applications de vision, de traitement de la parole, de radar, lidar et de communications. Le compilateur de réseaux de neurones Tensilica utilise un ensemble complet de bibliothèques de fonctions optimisées pour les réseaux neuronaux pour mapper n’importe quel réseau de neurones en un code de haute performance exécutable et hautement optimisé. Le processeur DNA 100 bénéficie en outre du soutien d’un écosystème logiciel robuste compatible avec différents types de réseaux (classification, détection d’objets, segmentation, récurrence et régression). Il prend également en charge l’API Android Neural Network (ANN) pour gérer l’inférence d’IA intégrée dans les appareils fonctionnant sous Android.

Le processeur DNA 100 peut piloter la totalité des couches des réseaux neuronaux (convolutifs, entièrement connectés, à mémoire court-terme persistante LSTM (Long Short-Term Memory), avec normalisation de réponse locale LRN (Local Response Normalization) et pooling). Un seul processeur DNA 100 peut facilement évoluer de 0,5 à 12 TMAC efficaces, plusieurs processeurs DNA 100 pouvant tre empilés afin d’atteindre des centaines de TMAC pour une utilisation dans les applications de réseaux neuronaux intégrées les plus gourmandes en puissance de calcul. Ce nouveau processeur embarque par ailleurs un DSP Tensilica qui prend en charge toute nouvelle couche de réseau neuronal non encore supportée par les moteurs matériels intégrés au processeur DNA 100, tout en offrant l’extensibilité et la programmabilité d’un cœur Tensilica Xtensa grâce aux instructions Tensilica Instruction Extension (TIE). Bénéficiant de son propre DMA (Direct Memory Access) , le processeur DNA 100 peut également exécuter d’autres codes de contrôle sans recourir à un contrôleur séparé.

Le processeur DNA 100 sera à la disposition de certains clients en décembre 2018 ; sa disponibilité générale est prévue au cours du premier trimestre 2019.

Fournisseur : Cadence

Référence : Tensilica DNA 100