Le CEA développe une mémoire hybride pour l’IA sur puce

Une équipe française dirigée par le CEA List et le CEA Leti a développé le premier circuit exploitant une technologie de mémoire non-volatile hybride, ouvrant la voie à l’apprentissage et l’inférence de l’IA directement sur puce.

Une équipe de chercheurs français dirigée par le CEA List et le CEA Leti affirme avoir levé un verrou technologique qui limite l’efficacité de l’apprentissage embarqué de l’IA, en mettant au point une architecture matérielle et des algorithmes dédiés qui permettent d’embarquer sur puce l’entraînement local adaptatif et l’inférence des réseaux de neurones artificiels, sans exploser la consommation énergétique, ni buter sur des contraintes matérielles.

L’IA embarquée exige à la fois l’inférence (la lecture des données pour prendre des décisions) et l’apprentissage (la mise à jour des modèles en fonction de nouvelles données). Mais jusqu’à présent, les technologies mémoire ne pouvaient réaliser correctement qu’une seule des deux tâches, comme l’explique l’équipe de chercheurs, dans un article récemment publié par Nature Electronics et intitulé « A Ferroelectric-Memristor Memory for Both Training and Inference ». « Les memristors (mémoires résistives non volatiles) excellent en inférence car leur endurance en lecture est quasi infinie et ils sont compatibles avec le calcul analogique en mémoire (IMC), qui réduit la consommation énergétique, tandis que les condensateurs ferroélectriques (FeCaps) excellent dans l’apprentissage sur puce grâce à leurs qualités en écriture (grande endurance et faible consommation d’énergie) », explique l’article.

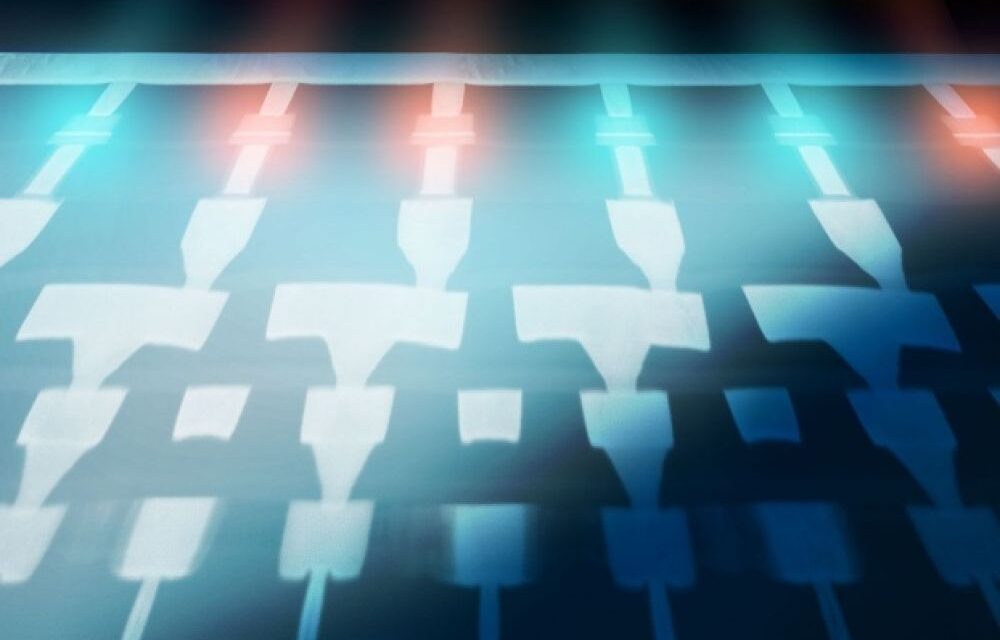

© E.VIANELLO-M.PLOUSEY DUPOUY/CEA

Pour lever ce verrou technologique, l’équipe a développé un nouveau système de mémoire hybride qui réunit les meilleurs atouts de deux technologies — les condensateurs ferroélectriques et les memristors — jusqu’alors incompatibles, au sein d’un empilement mémoire unique, compatible Cmos. Ce qui ouvre potentiellement la voie à des systèmes embarqués et des dispositifs tels que les véhicules autonomes, les capteurs médicaux et les moniteurs industriels, capables d’apprendre en temps réel à partir de données du monde réel, en adaptant leurs modèles à la volée, tout en maîtrisant strictement la consommation énergétique et l’usure matérielle.

Le défi consistait donc à intégrer sur un même wafer et à coût réduit deux technologies complémentaires. L’équipe a pour cela conçu un empilement mémoire unifiée à base d’oxyde d’hafnium dopé au silicium avec une couche de titane. Comme l’explique l’article, ce dispositif fonctionne nativement comme une FeCap mais l’application d’un stress électrique permet de former un filament conducteur, ce qui le transforme en OxRAM/memristor.

Il a ainsi été possible de concevoir une synapse hybride composée de FeCap numériques qui stockent une valeur précise du poids synaptique indispensable à l’apprentissage et de memristors analogiques utilisés principalement pour l’inférence.

Quant à l’algorithme d’apprentissage, il implique de mettre régulièrement à jour les poids des memristors avec la valeur des poids des FeCaps, ce qui a été réalisé grâce à une méthode de transfert numérique-analogique, sans convertisseur numérique-analogique formel, qui a été testée avec succès.

« Nous avons adopté un apprentissage inspiré des réseaux neuronaux binaires : la propagation des activations comme la rétropropagation du gradient sont calculées grâce aux memristors. Les FeCaps, elles, accumulent les mises à jour de poids à chaque échantillon d’apprentissage. Tous les 100 échantillons, le poids contenu dans les FeCaps et transféré dans les memristors, ce qui permet à l’apprentissage de converger efficacement », explique François Rummens, ingénieur chercheur au CEA List et co-auteur de la publication.

Concrètement, cette solution matérielle a été fabriquée et testée sur une matrice de 18 432 dispositifs en technologie Cmos 130 nm standard, intégrant sur une seule puce les deux types de mémoire ainsi que leurs circuits périphériques.