Rapidus installe le premier équipement EUV d’ASML au Japon

Le Japonais débute l’installation du premier équipement de lithographie EUV livré sur le sol japonais et destiné à la production de volume de semiconducteurs avancés en technologie 2 nm.

Rapidus, société créée en 2022 et soutenue par le gouvernement japonais et huit grandes entreprises nippones (Toyota, NTT, Sony, NEC, SoftBank, Denso, Kioxia et MUFG Bank) afin de remettre le Japon dans la course aux semiconducteurs les plus avancés, vient d’entamer une phase importante de la mise en place de son usine IIM-1 (Innovative Integration for Manufacturing) qu’il est en train de construire au Japon et qui exploitera des procédés de gravure en 2 nm.

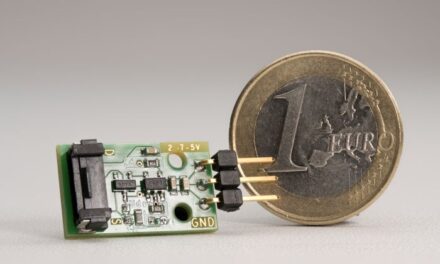

Rapidus vient ainsi d’annoncer la réception et le début de l’installation, sur son site de Chitose, du premier équipement de photolithographie aux UV extrêmes (EUV) livré sur le sol japonais et destiné à la production de volume de semiconducteurs avancés en technologie 2 nm. Il s’agit, en l’occurrence, du modèle NXE:3800E du Néerlandais ASML.

© Rapidus

Outre la machine de lithographie EUV, Rapidus installera dans sa fonderie IIM-1 d’autres équipements dédiés à la fabrication de semiconducteurs avancés, ainsi que des systèmes de manutention entièrement automatisés, afin d’optimiser la production de semiconducteurs exploitant la technologie GAA (gate-all-around) en 2nm. Une ligne pilote sera mise en service dans l’IIM-1 en avril 2025.

Rappelons que les nœuds de gravure en 2 nm et ceux de prochaine génération nécessitent une longueur d’onde très courte (13,5 nm) nécessitant des équipements de lithographie EUV dotés de sources laser, de systèmes optiques et des photomasques beaucoup plus précis que ceux utilisés précédemment. Le modèle NXE:3800E d’ASML installé dans la fonderie IIM-1 de Rapidus utilise notamment un système optique avancé avec un photomasque réfléchissant et des lentilles à miroir, et adopte une plateforme Twinscan qui effectue l’alignement et le balayage sur des étapes séparées, ce qui permet d’augmenter la productivité tout en répondant à la réduction de la taille des transistors.