Le CEA-Leti développe un processeur avec chiplets et interposeurs actifs

Le CEA-Leti, institut de CEA Tech, a présenté un démonstrateur de processeur de calcul haute performance à l’état de l’art mondial reposant sur un système multi-cœurs innovant modulaire, évolutif, économe en énergie et peu coûteux. Il repose sur l’assemblage modulaire de petits circuits (ou chiplets) en utilisant les technologies d’intégration 3D.

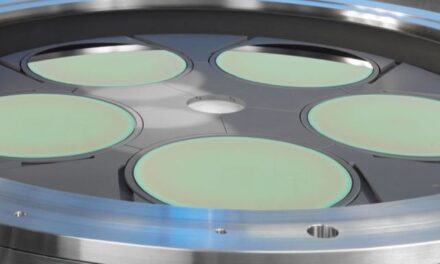

Utilisé dans de nombreuses industries à des fins de simulation par exemple, le calcul haute performance (ou HPC) consiste à combiner la puissance de plusieurs milliers de processeurs pour effectuer des calculs complexes ou des traitements de données massivement parallèles. Afin d’augmenter la capacité de calcul des processeurs multi-coeurs, le principe proposé pour faire le passage à l’échelle repose sur l’assemblage modulaire de petits circuits (ou chiplets) en utilisant les technologies d’intégration 3D. Cette approche permet de réduire les coûts de fabrication et d’assembler des fonctions hétérogènes dans une même structure (calcul, mémoire, interfaces, gestion de l’énergie, …).

Utilisé dans de nombreuses industries à des fins de simulation par exemple, le calcul haute performance (ou HPC) consiste à combiner la puissance de plusieurs milliers de processeurs pour effectuer des calculs complexes ou des traitements de données massivement parallèles. Afin d’augmenter la capacité de calcul des processeurs multi-coeurs, le principe proposé pour faire le passage à l’échelle repose sur l’assemblage modulaire de petits circuits (ou chiplets) en utilisant les technologies d’intégration 3D. Cette approche permet de réduire les coûts de fabrication et d’assembler des fonctions hétérogènes dans une même structure (calcul, mémoire, interfaces, gestion de l’énergie, …).

Jusqu’ici, les chiplets étaient assemblés sur un interposeur silicium passif, faisant le lien entre eux par de simples pistes métalliques, ce qui limitait les échanges entre les cœurs de calcul. Dans le cadre de l’IRT Nanoélec, le CEA-Leti, institut de CEA Tech, a développé un interposeur actif contenant une structure complète de communication intelligente. Ainsi, les chiplets peuvent communiquer entre eux directement et sans contrainte, quelles que soient leurs positions relatives dans l’assemblage. Cette nouvelle architecture augmente les performances en facilitant la communication et en offrant la possibilité de mettre un bien plus grand nombre de chiplets dans un même dispositif. Elle permet, enfin, d’intégrer des fonctions annexes au plus proche des cœurs de calcul pour différencier le système à la demande, explique le laboratoire dans un communiqué.

Un démonstrateur de 96 cœurs organisés en 6 chiplets en technologie FD-SOI, eux-mêmes intégrés en 3D sur un interposeur actif en silicium 65 nm, a été présenté à la conférence ISSCC à San Francisco en février 2020. Les applications potentielles sont nombreuses, en particulier pour intégrer des fonctions d’intelligence artificielle embarquée dans les véhicules autonomes, souligne le laboratoire du CEA.