Les SoC à cœurs RISC-V d’Andes Technology vont intégrer la technologie eFPGA de QuickLogic

L’intégration de la technologie eFPGA dans les sous-systèmes basés sur les processeurs à cœurs RISC-V offre aux développeurs la liberté d’apporter des modifications post-fabrication à leurs conceptions.

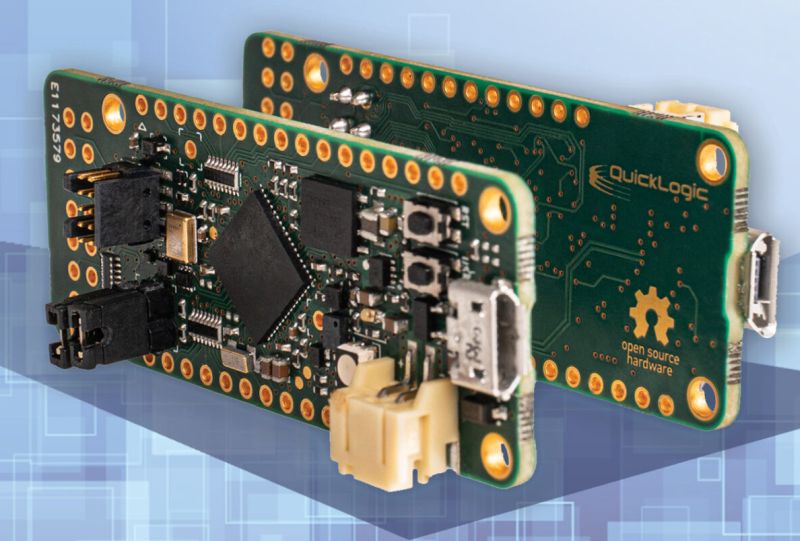

Le Taïwanais Andes Technology, spécialiste des processeurs 32 et 64 bits hautes performances et basse consommation à cœurs RISC-V sous forme d’IP, et le Californien QuickLogic, société fabless spécialisée dans les FPGA et les eFPGA (FPGA sous forme d’IP embarquée), annoncent un partenariat technologique qui permettra au premier d’intégrer dans ses SoC RISC-V les eFPGA du second.

Crédit photo : QuickLogic

L’ajout de la technologie eFPGA de QuickLogic aux SoC basés sur les cœurs RISC-V d’Andes Technology donnera aux développeurs la possibilité d’apporter des modifications post-fabrication à leurs conceptions. Cette flexibilité et cette évolutivité peuvent s’avérer particulièrement intéressantes pour ajouter la prise en charge de nouvelles normes, faire face à des menaces concurrentielles émergentes ou saisir de nouvelles opportunités de marché, l’idée sous-jacente étant de prolonger le cycle de vie des SoC et d’en améliorer la rentabilité de manière significative.

Rappelons que l’architecture AndeStar de cinquième génération d’Andes a adopté les cœurs RISC-V comme base. Ses familles de processeurs V5 RISC-V vont des petits cœurs 32 bits aux cœurs 64 bits avancés avec des capacités DSP, FPU, Vector, Linux, superscalaires et/ou multicœurs.

Les applications ciblées par les SoC RISC-V d’Andes sont vastes et comprennent les communications 5G, l’IoT, les équipements mobiles, les systèmes avancés d’assistance à la conduite (ADAS), l’intelligence artificielle (IA), la réalité augmentée/virtuelle (AR/VR), les centres de données, les réseaux à haut débit, etc.