Plateforme de développement autour de processeurs Arm Neoverse réalisée dans la technologie 7 nm de TSMC | Cadence, Xilinx

Cadence Design Systems et Xilinx annoncent la disponibilité d’une nouvelle plateforme de développement validée dans la filière 7 nm FinFET de TSMC pour infrastructures « cloud-to-edge » basée sur la nouvelle plateforme Neoverse N1 d’Arm. La plateforme de développement de système Neoverse N1 SDP (System Development Platform) est également la première plateforme de développement d’infrastructure en 7 nm de l’industrie à accélérer les calculs asymétriques via l’architecture d’interconnexion CCIX. Elle est proposée dès aujourd’hui aux développeurs pour les opérations de prototypage de matériels, développement de logiciels, validation au niveau système, profilage et réglage des performances.

La plateforme SDP se compose d’un système sur puce (SoC) architecturé autour d’un processeur Neoverse N1 dont la fréquence de cadencement peut atteindre 3 GHz, de caches importants et d’une généreuse bande passante mémoire avec la dernière IP système optimisée. La robustesse de la plateforme SDP convient au développement, au débogage, à l’optimisation des performances et à l’analyse de la charge de travail d’une large gamme d’applications, dont celles pour l’apprentissage automatique (machine learning), l’intelligence artificielle (IA) et l’analyse de données.

Développée conjointement par Arm, Cadence et Xilinx dans la filière de TSMC, la plateforme Neoverse N1 SDP inclut des blocs de propriété intellectuelle (IP) de Cadence pour CCIX, PCI Express (PCIe) Gen 4 et DDR4 PHY. Elle a été mise en œuvre et vérifiée à l’aide d’un flot d’outils Cadence complet réalisé dans la technologie FinFET 7 nm de TSMC — la première technologie de fabrication en 7 nm de l’industrie utilisée pour la production en série —, et assure la connexion aux circuits logiques programmables sur site (FPGA) Xilinx Virtex UltraScale+ à l’aide du protocole d’interconnexion cohérente entre puces CCIX via la carte d’accélération Alveo U280 de Xilinx. Pour les clients dont la charge de calcul est intense, le protocole CCIX améliore sensiblement la facilité d’utilisation des accélérateurs tout en améliorant les performances et l’efficacité des centres de données. Cette approche simplifie l’accès aux systèmes d’infrastructure de serveurs existants et réduit le coût total de possession (TCO) des systèmes d’accélération.

La plateforme de développement de système Neoverse N1 SDP sera disponible en quantités limitées au deuxième trimestre 2019 avant d’être élargie au cours des trimestres suivants. La suite logicielle est accessible via les référentiels open-source Linaro et GitHub, offrant aux développeurs une expérience logicielle Linux immédiatement opérationnelle. La carte d’accélération Xilinx Alveo U280, qui embarque un circuit logique programmable sur site FPGA haute performance avec mémoire large bande HBM (High-Bandwidth Memory) intégrée et interface CCIX, est disponible dès maintenant directement chez Xilinx.

De plus, les flots complets de mise en œuvre et de vérification des systèmes sur puce proposés par Cadence, ainsi que les blocs IP CCIX, PCIe Gen 4 et DDR4, et le kit d’adoption rapide (RAK) Neoverse N1, sont disponibles dès maintenant pour permettre aux clients de concevoir des systèmes sur puce Neoverse N1 dans la filière silicium 7 nm de TSMC.

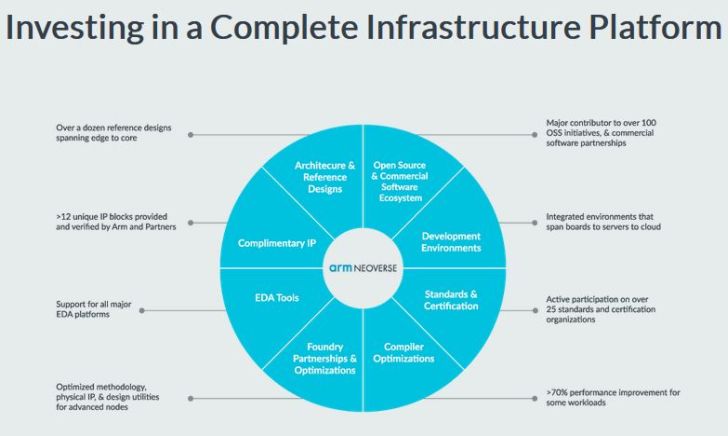

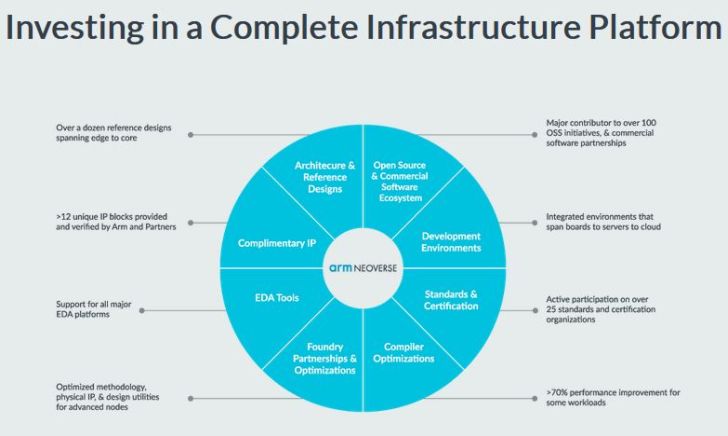

Plus d’informations sur la plateforme Neoverse N1