Semiconducteurs : une start-up britannique veut réhabiliter les anciennes fab

La jeune pousse de Nottingham SFN (Search for the Next) affirme avec mis au point un procédé de fabrication de semiconducteurs permettant de produire des circuits intégrés aussi performants que les circuits Cmos actuels, mais à partir de fab d’ancienne génération…

« Jusqu’au procédé Bizen, au transistor Zpolar et à la logique ZTL [Zpolar Tunnel Logic, ndlr], les puces hautes performances pour des applications telles que la 5G ne pouvaient être produites que dans des installations telles que celles du géant taïwanais TSMC, qui contrôle la plupart de la production mondiale de semiconducteurs hautes performances. Désormais, les fabs britanniques et occidentales peuvent redevenir compétitives et même dépasser les géants taïwanais et coréens, tout en garantissant les meilleurs intérêts nationaux. »

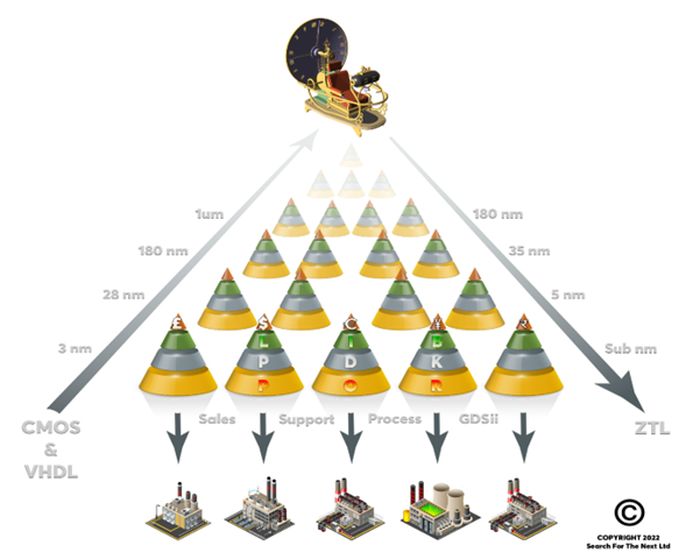

C’est en ces termes pour le moins ambitieux que David Summerland, Pdg de SFN (Search for the Next), une jeune entreprise britannique de Nottingham créée en 2017, présente ses nœuds de process baptisés ITM (Infrastructure Time Machine) qui combinent le procédé Bizen, les transistors Zpolar et la logique ZTL susnommés. Ces nœuds permettraient, à partir d’usines exploitant des géométries d’un autre temps (par exemple du 180 nm, voire du 1 µm), de produire des circuits intégrés avec des performances équivalentes à celles des composants Cmos fabriqués actuellement dans les usines de dernière génération.

Et David Summerland de citer l’exemple de l’usine 180 nm Newport Wafer Fab – la plus grande usine de production de semiconducteurs du Royaume-Uni actuellement au centre d’une guerre politico-commerciale concernant son projet de vente à la société chinoise Nexperia – qui pourrait produire des composants ZTL avec des performances (taille, vitesse, etc.) équivalentes à du Cmos 35 nm en mettant en œuvre l’un des nœuds ITM de SFN, et cela à un coût extrêmement réduit.

SFN propose d’ailleurs quatre ITM à son catalogue. L’ITM180 peut fournir des puces ZTL avec les performances d’un procédé Cmos 180 nm en utilisant un équipement pour nœuds de 1 µm. L’ITM35 permet de fabriquer des circuits intégrés équivalents Cmos 35 nm dans des fabs 180 nm. L’ITM5 autorise des performances Cmos de 5 nm à partir d’un procédé 28 nm. Quant à l’ITMSubnm, c’est la promesse, selon SFN, que les usines de fabrication de pointe actuelles de 3 nm seront en mesure de fournir des performances équivalentes à des structures sous le nm.

SFN précise que le VHDL est intégré à l’ITM sélectionné (en fonction des exigences de performances) par les concepteurs de puces, et que l’ITM, qui contient les bibliothèques de composants entièrement caractérisées (LIB) et le kit de développement de processus (PDK), fournit à la fois le processus de référence (POR) et les informations GDSii aux fonderies pour fabriquer la puce ZTL.

David Summerland, Pdg de SFN

La start-up explique que Bizen applique la mécanique quantique à toute technologie de process de wafers et que les puces Bizen ZTL demandent beaucoup moins de couches de process, ce qui permet de fabriquer des composants complexes dans des fabs utilisant une géométrie plus large. « Une fab 180 nm utilisant l’ITM35 pour fournir des puces ZTL avec des performances équivalentes à un Cmos 35 nm aura dix fois moins d’étapes de process qu’un process Cmos 35 nm classique, ce qui entraînera une réduction de 10 fois du temps de production. Cela se traduit par une multiplication par 40 à 50 du bénéfice net de la fab convertie à Bizen, affirme David Summerland. En même temps, cela contribuera massivement à résoudre les pénuries de semiconducteurs et à réduire notre dépendance en la matière vis-à-vis des puissances étrangères. »

Bizen est en développement dans une fab britannique depuis quatre ans et SFN a produit des wafers de test «gold standard» qui ont été caractérisés. Les données de caractérisation extraites ont été placées dans un livre de données JMP et utilisées pour produire des modèles SPICE qui s’exécutent dans l’environnement de conception Cadence et correspondent aux résultats de flux du process de wafers de Synopsis.