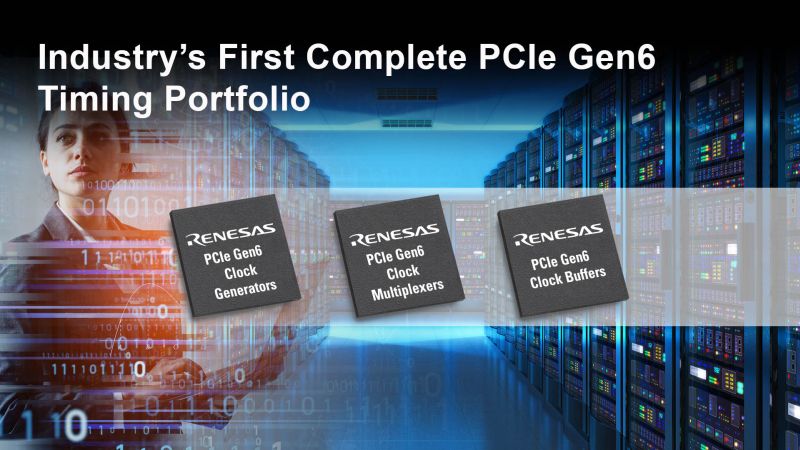

Renesas lance les premiers buffers d’horloge et multiplexeurs PCIe Gen6

Ces composants sont conformes aux spécifications strictes PCIe Gen6, un standard qui prend en charge des taux de transferts de 64 GT/s et nécessite une gigue d’horloge de moins de 100 fs rms.

Renesas Electronics commercialise respectivement sous les références RC190xx et RC192xx, ce qu’il estime être les premiers buffers d’horloge et multiplexeurs conformes aux spécifications strictes PCIe Gen6, un standard qui prend en charge des taux de transferts de 64 GT/s et nécessite une gigue d’horloge de moins de 100 fs rms.

Également compatible avec le standard PCIe Gen5 auquel elle apporte une marge supplémentaire, cette gamme, qui comprend onze buffers d’horloge et quatre multiplexeurs, vient compléter les générateurs d’horloge à faible gigue 9SQ440, 9FGV1002 et 9FGV1006 du Japonais, eux aussi compatibles PCIe Gen6, et s’adresse aux centres de données, au cloud computing, ainsi qu’aux réseaux télécoms et industriels.

Parmi les caractéristiques notables des séries RC190xx et RC192xx, signalons une gigue très faible de seulement 4 fs, un délai d’entrée-sortie de 1,4 ns, un décalage de sortie de 35 ps et un taux de réjection de l’alimentation (PSRR) de -80 dB à 100 kHz.

Les buffers RC190xx sont proposés dans des configurations à 4, 8, 13, 16, 20 et 24 sorties, tandis que les multiplexeurs RC192xx se déclinent en versions à 2, 4, 8 et 16 sorties. Ces composants sont par ailleurs très compacts, avec des boîtiers aussi petits que 3 x 3 mm, soit un encombrement réduit de 30% par rapport aux précédents composants de Renesas.

Ils intègrent également diverses fonctions utiles telles que les adresses SMBus sélectionnables pour une utilisation aisée de plusieurs composants et la protection en écriture SMBus pour améliorer la sécurité du système, une sortie Loss-Of-Signal (LOS) prenant en charge la surveillance et la redondance du système, une interface Side-Band à 4 fils pour l’activation et la désactivation de la sortie série haute vitesse et la connexion en « daisy-chain » des composants, ou bien encore les fonctions Power Down Tolerant (PDT) et Flexible Start-up Sequencing (FSS) qui garantissent un bon comportement du système dans des conditions anormales.