SK Hynix et TSMC unissent leurs forces pour développer des mémoires HBM4

Le Sud-Coréen a signé un protocole d’accord avec le fondeur de semiconducteurs pour travailler ensemble sur les mémoires HBM de nouvelle génération, avec l’intention de produire en volume des puces HBM4 dès 2026.

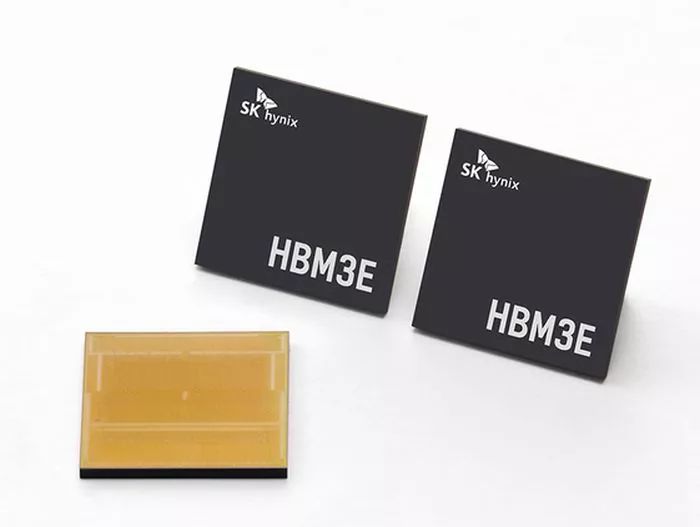

Alors que la production de volume des mémoires HBM3E, la 5è génération de mémoires HBM (High Bandwidth Memory) après les déclinaisons HBM, HBM2, HBM2E, HBM3, vient tout juste d’être lancée, la course au développement des mémoires HBM4 fait déjà rage avec des acteurs comme SK Hynix, Samsung, ou encore Micron. Il faut dire que ces mémoires à large bande passante et faible latence sont les candidates idéales pour les applications de calcul haute performance (HPC), notamment celles faisant intervenir des algorithmes d’IA.

Actuellement en pointe sur ce créneau (il a récemment affirmé être le premier à produire en volume des mémoires HBM3E), le Sud-Coréen SK Hynix ne compte pas se reposer sur ses lauriers et vient de signer un protocole d’accord avec TSMC pour produire dès 2026 des mémoires HBM4 et améliorer l’intégration des puces HBM grâce à une technologie d’encapsulation avancée.

© SK Hynix

Cet accord semble marquer une évolution dans la stratégie de SK Hynix qui, jusqu’ici, exploitait une technologie propriétaire pour fabriquer ses puces HBM jusqu’aux versions HBM3E. Mais avec cette collaboration avec le numéro un mondial de la fonderie de semiconducteurs et l’adoption du processus logique avancé de TSMC pour la puce de base de ses futures mémoires HBM4, SK Hynix compte intégrer des fonctionnalités supplémentaires dans un espace limité et développer des innovations permettant une amélioration des performances des mémoires grâce à une coopération plus étroite entre les concepteurs du produit, la fonderie et le fournisseur de mémoires.

« Nous espérons qu’un partenariat solide avec TSMC nous aidera à accélérer nos efforts de collaboration ouverte avec nos clients et à développer les mémoires HBM4 les plus performantes du marché, précise Justin Kim, président et responsable d’AI Infra chez SK Hynix. Avec cette coopération, nous renforcerons encore notre leadership sur ce marché en tant que fournisseur des mémoires dédiées aux applications exploitant l’IA. »

Les deux sociétés se concentreront en premier lieu sur l’amélioration des performances de la puce de base montée tout en bas du boîtier HBM. Rappelons que les mémoires HBM interconnectent verticalement plusieurs puces Dram via la technologie TSV (through silicon via) afin d’améliorer considérablement la vitesse de traitement des données par rapport aux mémoires Dram conventionnelles.

SK Hynix et TSMC ont également convenu d’optimiser l’intégration de la technologie HBM de SK hynix et le procédé CoWoS (Chip on Wafer on Substrate) de TSMC. CoWoS est une méthode d’encapsulation propriétaire de TSMC qui connecte un processeur, une puce logique et une mémoire HBM sur un substrat spécial appelé interposeur. TSMC parle ici de packaging 2,5D dans la mesure où la puce logique et la mémoire HBM et ses couches empilées (3D) sont intégrées dans un module placé sur un substrat de boîtier horizontal (2D).