Vérification physique pour la photonique sur silicium : ne paniquez pas !

Par Omar El-Sewefy, responsable technique DRC dans la division Design to Silicon de Mentor, une entreprise de Siemens.

Introduction

La photonique sur silicium offre une amélioration par rapport aux signaux électriques traditionnels dans les circuits intégrés (CI) grâce à la transmission de lumière pour accélérer le transfert de données et réduire la consommation d’énergie. Selon MarketsandMarkets, le marché global de la photonique sur silicium s’est élevé à environ 774,1 millions de dollars en 2018 et devrait atteindre 1 988,2 millions d’ici 2023, pour un TCAC de 20,8 % entre 2018 et 2023[1]. Le Cloud Computing fait partie des marchés à l’origine d’une augmentation exponentielle du trafic de données, au même titre que les télécommunications, l’armée, la défense et l’aérospatiale. À la demande croissante de bande passante élevée et de capacités de transfert rapide de données dans les centres de données et les solutions de calcul intensif vient s’ajouter la nécessité de réduire la consommation d’énergie. Ensemble, ces facteurs stimulent la croissance du marché de la photonique sur silicium.

La photonique sur silicium offre une amélioration par rapport aux signaux électriques traditionnels dans les circuits intégrés (CI) grâce à la transmission de lumière pour accélérer le transfert de données et réduire la consommation d’énergie. Selon MarketsandMarkets, le marché global de la photonique sur silicium s’est élevé à environ 774,1 millions de dollars en 2018 et devrait atteindre 1 988,2 millions d’ici 2023, pour un TCAC de 20,8 % entre 2018 et 2023[1]. Le Cloud Computing fait partie des marchés à l’origine d’une augmentation exponentielle du trafic de données, au même titre que les télécommunications, l’armée, la défense et l’aérospatiale. À la demande croissante de bande passante élevée et de capacités de transfert rapide de données dans les centres de données et les solutions de calcul intensif vient s’ajouter la nécessité de réduire la consommation d’énergie. Ensemble, ces facteurs stimulent la croissance du marché de la photonique sur silicium.

Cependant, cette demande croissante de circuits intégrés photoniques (CIP) accroît également le besoin d’une plate-forme de vérification physique solide et stable pour les conceptions CIP. La disparité entre la conception et la fabrication de circuits intégrés électroniques (CIE) traditionnels, avec leurs processus et outils de vérification éprouvés et établis de longue date, et les nouveaux CIP, qui introduisent de nouvelles exigences de vérification , offre aux entreprises spécialisées dans les solutions d’automatisation de la conception électronique (EDA) la possibilité de proposer des solutions innovantes. En trouvant de nouvelles façons d’utiliser les outils existants, ils créent des flots de vérification qui peuvent évaluer le comportement électrique et optique des CIP, tout comme les flots de vérification existants pour les CIE.

Conception de circuits photoniques sur silicium

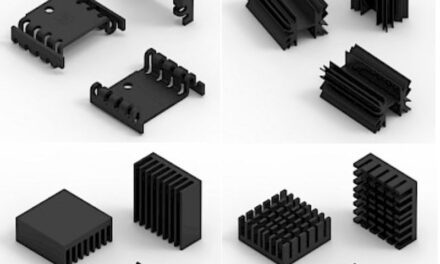

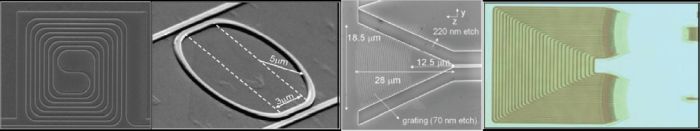

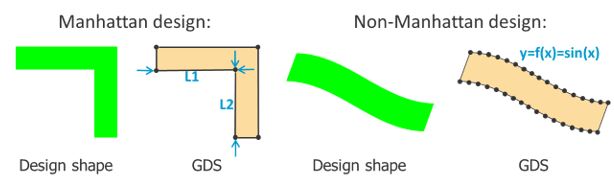

Un élément fondamental distingue les CIP des CIE : la construction géométrique des composants de base. Les CIE utilisent une topologie de type Manhattan. Les circuits sont conçus sur une grille rectangulaire qui ne permet que des angles de 0°, 45° et 90°. En revanche, les CIP comprennent une grande variété de structures curvilignes, telles que des lignes à retard, des résonateurs en anneau, des guides d’ondes, des coupleurs de réseau, etc. (Figure 1).

Figure 1. Composants courants des CIP (sources : IMEC et IHP ; reproduit avec autorisation).

En outre, les CIP n’utilisent pas les schémas de conception traditionnels, ce qui fait du concept de vérification LVS (layout vs. schematic) une notion étrangère aux concepteurs de circuits photoniques. Néanmoins, ils doivent toujours être en mesure de s’assurer que les ports des circuits photoniques sont correctement connectés aux nœuds des circuits électroniques et permettre la reconnaissance des circuits et de leurs paramètres.

Défis liés à la vérification physique des CIP

Les concepteurs mesurent l’intégrité géométrique d’un CIE à l’aide de la vérification des règles de conception (DRC), qui détermine si le layout physique respecte les exigences de fabrication (règles de conception) établies par la fonderie. Comme les CIE traditionnels se composent de formes Manhattan placées sur une grille rectangulaire, la mesure des divers paramètres géométriques est assez simple, et la précision peut être relativement élevée.

Dans les CIP, le fait de placer des structures curvilignes sur une grille rectangulaire représente un défi pour les outils existants de vérification des CI et les process de fabrication(Figure 2).

La précision des mesures est problématique en raison du « snapping » des géométries (bords et sommets), qui se produit lorsque les points des formes courbes doivent s’adapter à la résolution de la cartographie linéaire, ce qui donne lieu à une approximation imprécise.

Figure 2 : Défis associés à la vérification physique des structures curvilignes.

Pour obtenir des résultats plus précis, cet effet doit être compensé pendant les mesures des paramètres géométriques. L’extraction et la validation de ces formes non traditionnelles nécessitent de nouveaux paramètres, tels que la courbure de flexion et la longueur du trajet curviligne. Il n’est pas réaliste de reconstruire ou de réinventer tout un ensemble d’outils et un flot de vérification des CIP pour les adapter à de telles structures, compte tenu du temps et des ressources que cela impliquerait. Par ailleurs, les fournisseurs de solutions de CAO électronique (EDA) ont développé de nouvelles techniques de vérification des CIP capables d’atteindre le degré de précision requis en apportant des modifications relativement simples aux ensembles d’outils existants pour les CIE.

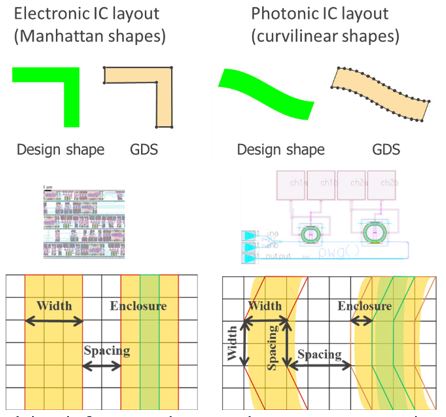

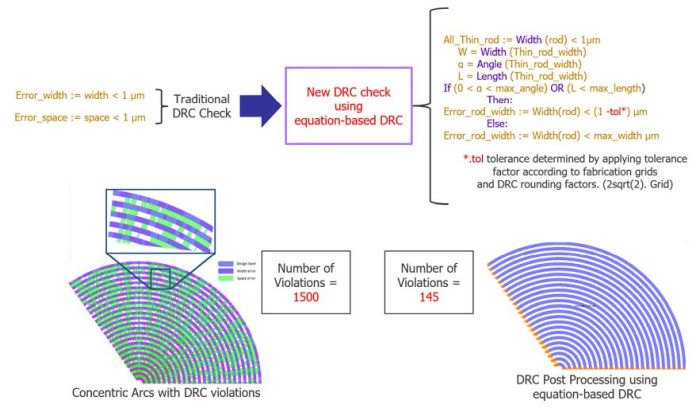

La DRC basée sur des équations représente un ajout utile à l’ensemble d’outils de vérification des CIP. Cette méthode peut appliquer la DRC conditionnelle complexe avec des valeurs de tolérance multidimensionnelles au lieu des calculs arithmétiques traditionnels de la DRC. Sans la DRC basée sur des équations, la vérification physique des CIP génère de nombreuses fausses erreurs, principalement dues à des erreurs d’arrondi ou de cassure des bords pendant les mesures (Figure 3).

Figure 3 : L’utilisation de la DRC traditionnelle sur des structures curvilignes crée de nombreuses fausses erreurs[2].

Pour éliminer ces fausses violations, les concepteurs ajoutent la DRC basée sur des équations aux contrôles DRC traditionnels afin de détecter les segments courbes de la conception et appliquer les facteurs de tolérance nécessaires pour éliminer les fausses erreurs. L’introduction du filtrage et de la vérification basés sur des équations permet d’offrir toute une nouvelle gamme de capacités de DRC pour la photonique sur silicium, dans lesquelles les équations multidimensionnelles peuvent être évaluées pour vérifier avec précision la validité géométrique des circuits photoniques (Figure 4).

Figure 4 : L’utilisation de fonctionnalités basées sur des équations sur des structures curvilignes réduit les fausses violations[2].

Cependant, comme la longueur maximale des bords diminue, il faut plus de bords pour représenter un seul polygone. La durée d’exécution des vérifications augmente de façon proportionnelle avec le nombre de bords, car les outils de vérification DRC se basent sur les bords. Les concepteurs doivent gérer les conflits liés à l’utilisation d’un grand nombre de bords pour représenter avec précision les composants des CIP par rapport à l’impact possible sur l’exécution. Pour effectuer la DRC appropriée du layout des CIP, de nombreux concepteurs de CIP ont adopté un nouveau style de codage, dans lequel la longueur maximale des bords joue un rôle important dans la possibilité d’ajuster les performances par rapport à l’exactitude des résultats.

Dans certains outils de vérification physique, l’exécution de la DRC basée sur des équations peut ne pas avoir d’impact significatif, en raison des multiples stratégies d’optimisation de l’exécution intégrées à l’outil. Cet impact doit néanmoins toujours être pris en compte lors du développement de kits de conception de processus (PDK) de DRC pour la photonique sur silicium.

Défis associés à la vérification des circuits CIP

L’absence d’une netlist de sources SPICE constitue un autre défi dans la création d’un flot de conception de CIP. La capture et la simulation des schémas des CIE (conception, layout automatisé, LVS, extraction de parasites [PEX], re-simulation, etc.) dépendent fortement de la simulation de circuits SPICE, mais il n’existe aucune approche générique équivalente pour la simulation des CIP. Les outils de type CAO technologique (TCAD) sont généralement utilisés pour leur précision, mais leurs capacités/performances sont limitées en raison de l’absence d’un format commun pour la vérification et la validation dans l’ensemble du flot.

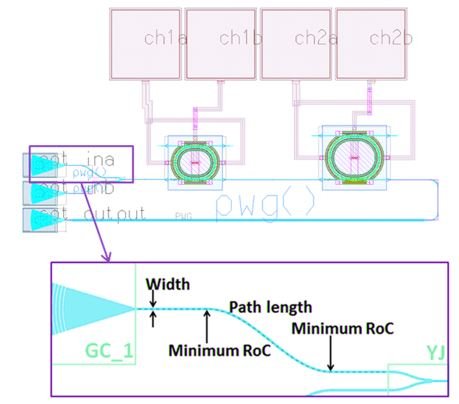

Dans les CIP, les guides d’ondes agissent comme une interconnexion optique entre les différents composants du circuit, mais représentent également les composants de base de la plupart des CIP. Contrairement à l’interconnexion dans les CIE, les guides d’ondes doivent être traités comme des éléments plutôt que comme une interconnexion idéale, en raison de la différence dans le concept de connectivité en photonique. Les paramètres d’un guide d’ondes jouent un rôle central dans son fonctionnement, en raison de leur impact sur les modes de propagation des guides d’ondes. De plus, les concepts électroniques simples tels que court-circuit et circuit ouvert sont différents dans la conception photonique. Par exemple, deux guides d’ondes peuvent se chevaucher, créant ainsi un réseau à quatre ports, sans entraîner une interconnexion court-circuitée (Figure 5).

Figure 5 : Extraction des paramètres du CIP dans la vérification LVS.

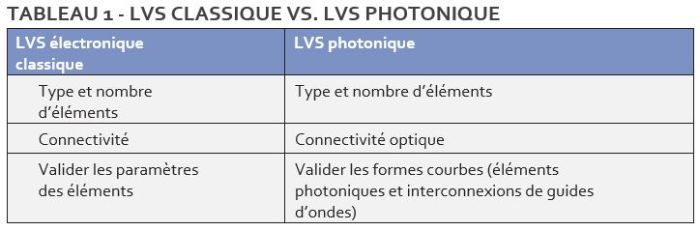

La comparaison d’un flot de LVS électronique classique aux exigences de la LVS photonique peut aider à déterminer les composants LVS manquants, à savoir la connectivité optique et la validation des formes de conception courbes (Tableau 1). La connectivité optique et la fonctionnalité des circuits photoniques sont validées par l’extraction et la comparaison des paramètres : largeur, longueur du trajet curviligne et courbure de flexion. La contrainte réside dans le fait que nous devons supposer un type de courbe pour ladite courbe (par exemple, arc circulaire, Bessier, adiabatique, etc.).

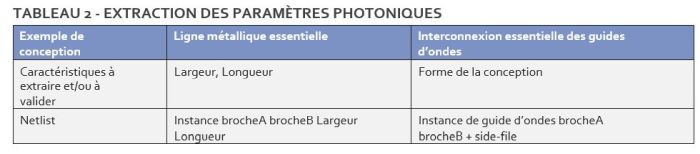

La vérification LVS traditionnelle extrait la courbure supposée et l’associe à une source. La LVS avec correspondance de formes, nouvelle méthode de validation des conceptions curvilignes, commence par la source et valide la courbure (Figure 6). Le tableau 2 décrit la différence, en termes d’extraction des paramètres, entre la LVS traditionnelle et la LVS avec correspondance de formes.

Figure 6 : LVS avec correspondance de formes.

On trouve plusieurs méthodes pour la correspondance de formes :

On trouve plusieurs méthodes pour la correspondance de formes :

- Ré-instanciation de Pcell en superposition à l’emplacement prévu, suivi d’un OU exclusif, qui trouvera les différences/erreurs dues au placement.

- « Pattern matching », facile à mettre en œuvre, mais nécessitant au moins quelques bords Manhattan pour la correspondance. Il est également nécessaire de déterminer les tolérances autorisées et la façon d’extraire les paramètres à partir de ces tolérances.

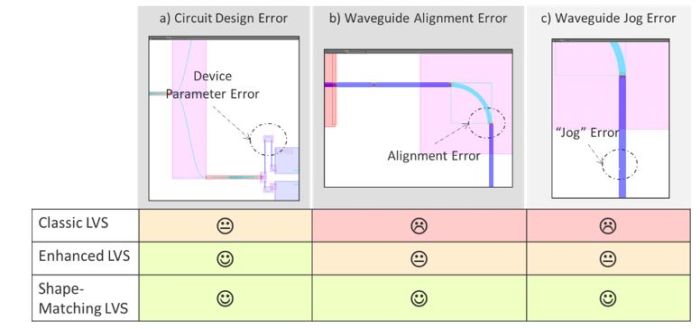

La Figure 7 compare la LVS classique, la LVS améliorée et la LVS avec correspondance de formes, montrant la couverture supérieure de la dernière méthode.

Figure 7 : Comparaison de différentes techniques de LVS pour la photonique sur silicium.

Simulation de conception après lithographie

Traditionnellement, les processus de conception de circuits intégrés, en particulier aux nœuds plus anciens, supposent que ce qui est dessiné est ce qui sera imprimé (du masque au silicium). Aux nœuds avancés, pour compenser la taille finie de l’objectif (qui ne saisit pas tout l’ordre de diffraction du masque), des techniques de lithographie telles que la correction optique de proximité (OPC) doivent être utilisées pour modifier le layout avant la fabrication afin de s’assurer qu’il correspond à l’intention originale dessinée.

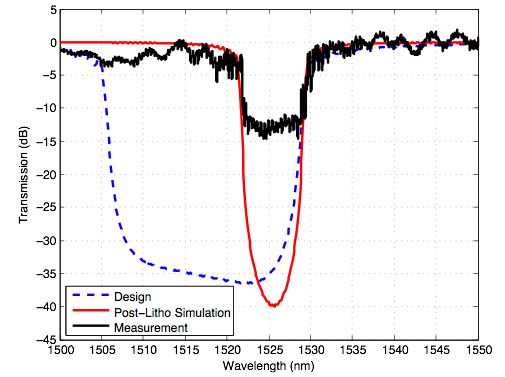

Pour les CIP, il est essentiel que les concepteurs modélisent correctement et précisément les formes finales du circuit, en raison de l’impact direct sur les performances du circuit. Pour les circuits multi-projets (MPW), les concepteurs ont généralement besoin de plusieurs itérations de fabrication de circuits physiques pour comprendre et améliorer le comportement du circuit (Figure 8). Cependant, l’itération physique prend beaucoup de temps et est extrêmement coûteuse.

Figure 8 : La largeur de bande du guide d’ondes de Bragg fabriqué est inférieure celle de l’intention de conception (reproduit avec l’autorisation de Xu Wang[3]).

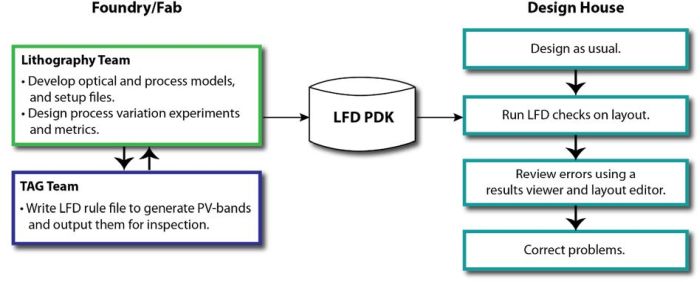

Les concepteurs peuvent également se servir des kits de conception de processus (PDK) fournis par la fonderie, qui incorporent les effets de lithographie. Les lithographes et les groupes d’accès aux technologies (TAG) des fonderies utilisent les outils de conception adaptés à la lithographie (LFD) proposés par les fournisseurs EDA pour développer ces PDK. L’utilisation d’un outil LFD avec un PDK LFD permet aux concepteurs d’effectuer une variété de contrôles de simulation du process auparavant réservés aux lithographes travaillant dans des fonderies de semi-conducteurs. Ces vérifications permettent d’identifier les problèmes potentiels de résolution lithographique avant le tapeout (Figure 9). Les équipes de conception peuvent ensuite appliquer les modifications ou les techniques OPC nécessaires pour garantir la fabrication et les performances. Avec un procédé lithographique virtuel automatisé, les concepteurs réduisent leurs délais de plusieurs mois tout en évitant de dépenser de l’argent pour du silicium qui ne répond pas à leurs attentes.

Figure 9 : Worflow LFD type.

Conclusion

Le marché croissant des circuits photoniques sur silicium a entraîné le besoin de flots de vérification physique et de vérification de la fabrication fiables et automatisés qui tiennent compte des caractéristiques physiques uniques des conceptions photoniques sur silicium. Heureusement, il n’est pas nécessaire de réinventer les outils et les processus déjà existants pour la vérification électronique des CI. En élargissant l’utilisation de fonctionnalités établies telles que la DRC basée sur des équations, la LVS avec correspondance de formes et la conception LFD, les concepteurs peuvent intégrer les nouveaux composants et concepts de conception de la photonique sur silicium.

Références

[1] MarketsandMarkets, “Silicon Photonics Market by Product (Transceiver, Switch, Variable Optical Attenuator, Cable, Sensor), Application (Data Center, Telecommunications, Military & Defense, Medical and Life Sciences, Sensing), Component, and Geography – Global Forecast to 2023” February 2018. https://www.marketsandmarkets.com/Market-Reports/silicon-photonics-116.html

[2] R. Cao, J. Ferguson, F. Gays, Y. Drissi, A. Arriordaz and I. O’Connor, “Silicon photonics design rule checking: Application of a programmable modeling engine for non-Manhattan geometry verification,” 2014 22nd International Conference on Very Large Scale Integration (VLSI-SoC), Playa del Carmen, 2014, pp. 1-6. doi: 10.1109/VLSI-SoC.2014.7004173

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=7004173&isnumber=70041501]

[3] X. Wang et al., « Lithography simulation for the fabrication of silicon photonic devices with deep-ultraviolet lithography, » The 9th International Conference on Group IV Photonics (GFP), San Diego, CA, 2012, pp. 288-290.

doi: 10.1109/GROUP4.2012.6324162

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6324162&isnumber=6324060

Auteur

Omar El-Sewefy est responsable technique DRC dans la division Design to Silicon de Mentor, une entreprise de Siemens. Il est titulaire d’un BS et d’un MS en ingénierie électronique de l’Université Ain Shams au Caire, en Égypte, et poursuit actuellement des études de doctorat à l’Université Ain Shams en vérification physique des circuits photoniques sur silicium. Avec 10 ans d’expérience dans les solutions de conception et de fabrication de semi-conducteurs, l’expertise d’Omar couvre les techniques d’amélioration de la résolution des semi-conducteurs (RET), l’optimisation des masques sources, la vérification des règles de conception et la vérification physique des circuits photoniques sur silicium. Il est joignable à l’adresse omar_elsewefy@mentor.com.

Omar El-Sewefy est responsable technique DRC dans la division Design to Silicon de Mentor, une entreprise de Siemens. Il est titulaire d’un BS et d’un MS en ingénierie électronique de l’Université Ain Shams au Caire, en Égypte, et poursuit actuellement des études de doctorat à l’Université Ain Shams en vérification physique des circuits photoniques sur silicium. Avec 10 ans d’expérience dans les solutions de conception et de fabrication de semi-conducteurs, l’expertise d’Omar couvre les techniques d’amélioration de la résolution des semi-conducteurs (RET), l’optimisation des masques sources, la vérification des règles de conception et la vérification physique des circuits photoniques sur silicium. Il est joignable à l’adresse omar_elsewefy@mentor.com.