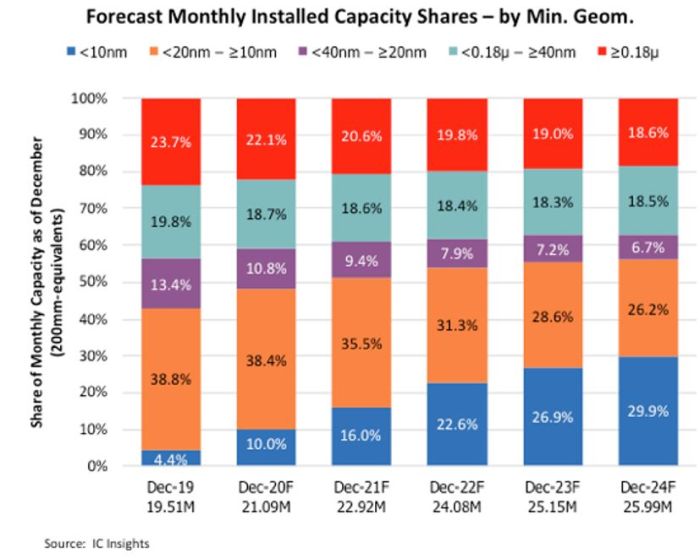

30% des capacités de production de puces pour des géométries de moins de 10 nm dès 2024

Selon IC Insights, les technologies de pointe (<10 nm) devraient représenter 29,9% de la capacité de production mondiale installée de circuits intégrés dès 2024, contre 10% à la fin de l’année et 4,4% en décembre 2019. Les procédés de fabrication de puces avec des géométries de moins de 10 nm deviendront ainsi la catégorie dominante dans quatre ans.

De nombreux facteurs poussent les fabricants de semiconducteurs à passer à des géométries de plus en plus fines : vitesse plus élevée, consommation d’énergie inférieure, coût par unité de surface plus faible, etc. Mais il arrive un moment où la diminution des rendements amène les concepteurs de puces à se demander si le coût élevé en vaut la peine, analyse IC Insights. Les coûts des équipements associés aux technologies inférieurs à 10 nm ont grimpé au point où ils sont devenus prohibitifs pour de nombreux fournisseurs de circuits intégrés. Par conséquent, seuls Samsung, TSMC et Intel exploitent actuellement des usines utilisant une technologie de processus <10 nm.

Dans le même temps, des difficultés de conception (par exemple, continuer à réduire les cellules de mémoires flash DRAM et NAND) entravent les méthodes de mise à l’échelle que l’industrie des circuits intégrés utilise depuis de nombreuses années. Les défis se posent également pour les puces logiques complexes telles que les microprocesseurs, les ASIC, les FPGA et d’autres dispositifs logiques avancés. IC Insights estime que le rythme de migration de tailles de fonctionnalités plus fines pour les puces logiques complexes continuera de ralentir car les concepteurs de puces ont de plus en plus de mal à justifier des coûts de production plus élevés. Pour les applications qui bénéficient grandement de vitesses plus élevées, d’une consommation d’énergie réduite, etc., il y aura une demande pour les procédés de fabrication finFET de pointe et au-delà. Le déploiement de générations en demi-étapes ou de versions améliorées des processus existants contribue également à augmenter la durée entre chaque nœud de nouvelle génération, explique le cabinet d’études américain.

En 2020, 48% de la capacité totale installée de production de semiconducteurs devrait concerner des dispositifs ayant des géométries inférieures à 20 nm (10% <10 nm ; 38,4% entre 10 et 20 nm). Ces composants comprennent des mémoires Drams haute densité et des mémoires flash NAND 3D haute densité avec une technologie équivalente de classe 10 nm, des microprocesseurs haute performance, des processeurs d’application basse consommation et des circuits intégrés de type ASIC / ASSP / FPGA avancés basés sur des technologies 16/14 nm, 12/10 nm, ou 7/5nm.

La Corée du Sud, avec 66% de sa capacité dédiée à des procédés <20 nm, reste nettement à la pointe de la technologie par rapport aux autres régions ou pays. Compte tenu de l’accent mis par Samsung et SK Hynix sur les mémoires Drams haute densité, les mémoires flash et les processeurs d’applications de Samsung, il n’est pas surprenant que le pays ait la plus forte concentration de processus de pointe, souligne IC Insights.

Apple, Huawei et Qualcomm utilisent les services de fonderie logique de pointe de TSMC. En conséquence, la capacité totale <20 nm de Taiwan s’élève à plus de 35%. Néanmoins, les générations 28nm, 45/40nm et 65nm continuent de générer des volumes d’affaires importants pour des fondeurs comme TSMC et UMC.

Enfin, la plupart des capacités <20 nm en Chine est détenue et contrôlée par des sociétés étrangères, telles que Samsung, SK Hynix, Intel et TSMC. YMTC et SMIC sont les seules entreprises nationales en Chine à faire appel à une technologie inférieure à 20 nm.