DSP pour applications de vision numérique et d’intelligence artificielle | Cadence

Cadence Design Systems étoffe sa famille de processeurs de signal numériques (DSP) Tensilica Vision avec le lancement de deux nouveaux cœurs IP DSP pour les applications d’intelligence artificielle et de vision embarquées.

Avec une puissance de calcul de 3,8 Téra-opérations par seconde (TOPS), le DSP Cadence Tensilica Vision Q8, fer de lance de cette famille de DSP, double les performances et la bande passante mémoire du DSP Tensilica Vision Q7 avec une efficacité énergétique élevée qui convient aux applications de vision numérique et d’imagerie haut de gamme utilisées par les marchés de l’automobile et de communications mobiles. Le DSP Tensilica Vision P1 est, quant à lui, optimisé pour les capteurs intelligents et les applications opérationnelles en permanence (always-on) que l’on trouve dans les applications d’électronique grand public auxquelles il apporte une solution efficace en consommation d’énergie.

Avec une puissance de calcul de 3,8 Téra-opérations par seconde (TOPS), le DSP Cadence Tensilica Vision Q8, fer de lance de cette famille de DSP, double les performances et la bande passante mémoire du DSP Tensilica Vision Q7 avec une efficacité énergétique élevée qui convient aux applications de vision numérique et d’imagerie haut de gamme utilisées par les marchés de l’automobile et de communications mobiles. Le DSP Tensilica Vision P1 est, quant à lui, optimisé pour les capteurs intelligents et les applications opérationnelles en permanence (always-on) que l’on trouve dans les applications d’électronique grand public auxquelles il apporte une solution efficace en consommation d’énergie.

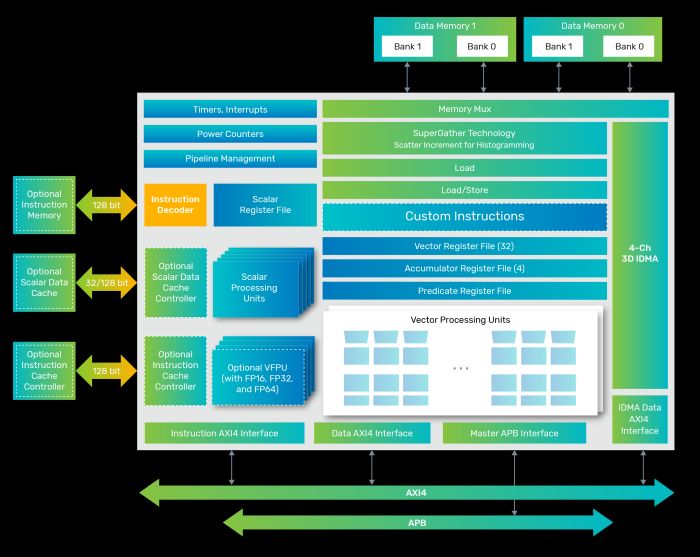

Basés sur une architecture à instruction unique et données multiples (SIMD — Single Instruction on Multiple Data) et à mot d’instruction très long (VLIW — Very Long Instruction Word) similaire à celle dont disposent les DSP Tensilica Vision déjà disponibles, les DSP Vision Q8 et Vision P1 utilisent un modèle de programmation générique (N-way programming model) qui préserve la compatibilité logicielle avec les DSP Tensilica Vision de précédente génération qui traitent un nombre différent de données par cycle de calcul.

Comme avec les autres DSP de Tensilica, les clients peuvent personnaliser à leur gré le jeu d’instructions des DSP Vision Q8 et Vision P1 grâce au langage d’extension d’instructions TIE (Tensilica Instruction Extension). Ces deux DSP sont également compatibles avec le compilateur de réseaux neuronaux Xtensa (XNNC — Xtensa Neural Network Compiler) et l’API Android Neural Networks (NNAPI) pour réseaux neuronaux. En outre, ils supportent plus de 1700 fonctions compatibles avec la librairie OpenCV, le langage OpenCL et le compilateur Halide pour le développement efficace des applications de vision et d’imagerie numérique. Ces deux cœurs IP de semiconducteur sont parés pour les applications d’électronique automobile et certifiés aux niveaux d’intégrité ASIL B pour les défaillances matérielles aléatoires et ASIL D pour les défaillances systématiques.

Le DSP Tensilica Vision Q8 qui implémente la septième génération de l’architecture et du jeu d’instructions dispose des caractéristiques et capacités suivantes:

• Conçu et optimisé pour les applications automobiles multi-caméras et mobiles haut de gamme ;

• Avec une capacité de calcul de 3,8 TOPS, l’architecture SIMD 1024 bits double les performances des applications de vision numérique, d’IA et de calcul en virgule flottante avec une bande passante mémoire multipliée par deux par rapport au DSP Vision Q7

• L’utilisation d’une seule instance du cœur IP permet de simplifier la conception au niveau système et de minimiser la consommation d’énergie jusqu’à 20 %

• Amélioration des performances par 4 pour le traitement des couches non convolutives de réseaux de neurones pour les applications d’intelligence artificielle

• Le jeu d’instructions a été étendu pour faciliter et optimiser le développement d’application logicielle à partir des langages évolués OpenCL et Halide,

• le jeu d’instructions peut être utiliser afin de développer des programmes de manière générique, ce qui permet d’écrire le code une fois et de le réutiliser par la suite sur d’autres DSP Tensilica Vision dont l’architecture SIMD peut être de différente largeur.

Pour sa part, le DSP Tensilica Vision P1 proposent les caractéristiques et capacités principales suivantes :

• Conçu et optimisé pour les applications actives en permanence (always-on), telles que les capteurs intelligents, les lunettes de réalité augmentée/virtuelle (RA/RV), les appareils connectés à l’Internet des objets et la domotique

• L’architecture SIMD 128 bits permet d’exécuter 400 gigaopérations par seconde (GOPS) pour un tier de la puissance dissipée et un tier de la taille du DSP Vision P6 largement adopté dans l’industrie, à une fréquence supérieure de 20% ;

• L’architecture est optimisée pour une faible occupation de la mémoire et un fonctionnement en mode basse consommation de puissance

Le DSP Tensilica Vision Q8 est disponible immédiatement ; le DSP Tensilica Vision P1 devrait être commercialisé au deuxième trimestre 2021.

Ces processeurs, qui complètent le portefeuille de DSP dédiés aux applications de vision numérique et d’intelligence artificielle de Cadence, assurent aux clients de la société une flexibilité de conception accrue accompagnée d’une technologie de pointe implémentée dans nombreux circuits intégrés.

Plus d’informations sur les DSP Vision Q8 et Vision P1