Keysight lance un outil de simulation des interconnexions de chiplets

Chiplet PHY Designer est le premier outil du marché à proposer des capacités de modélisation et de simulation approfondies, permettant la vérification rapide et précise de la conformité à l’UCIe.

La norme Universal Chiplet Interconnect Express (UCIe) s’impose comme la principale spécification d’interconnexion entre les circuits intégrés hétérogènes et 3D, ou chiplets, au sein d’un boîtier 2,5D ou 3D avancé, dans l’industrie des semi-conducteurs.

Cette norme ouverte est en passe d’être pris en charge ou adopté par un grand nombre des principaux fournisseurs d’équipements de semi-conducteurs et d’outils de CAO électronique, ainsi que par les fonderies et les concepteurs de chiplets.

Cette norme ouverte est en passe d’être pris en charge ou adopté par un grand nombre des principaux fournisseurs d’équipements de semi-conducteurs et d’outils de CAO électronique, ainsi que par les fonderies et les concepteurs de chiplets.

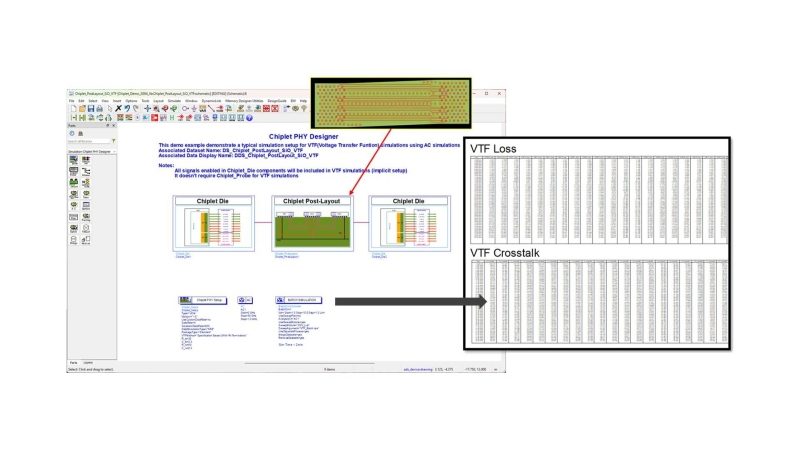

L’Américain Keysight Technologies vient d’ajouter à sa famille d’outils de conception et de simulation numériques le logiciel Chiplet PHY Designer W3650B. Il permet la simulation d’interconnexion de puce à puce (D2D), une étape clé dans la vérification des performances des designs de chiplets. Il est surtout le premier outil du marché à proposer des capacités de modélisation et de simulation approfondies, qui permettent aux concepteurs de vérifier rapidement et avec précision la conformité de leurs designs à la spécification UCIe.

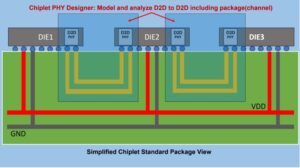

Avec le simulateur de couche physique Chiplet PHY Designer, les utilisateurs bénéficient de la prise en charge de la norme de couche physique UCIe, avec l’analyse automatique des signaux selon les conventions de dénomination standard, les connexions automatisées entre plusieurs matrices via des interconnexions de boîtiers, la configuration de simulation standard telle que la vitesse, et la configuration de mesure via un composant de sonde spécialisé.

Parmi les autres fonctionnalités, on trouve la mesure de la fonction de transfert de tension (VTF) – le calcul précis d’une VTF, l’analyse du taux d’erreur binaire (BER) du système jusqu’à des niveaux de 1.e-27 ou 1.e-32, et la mesure de la hauteur et de la largeur du diagramme de l’œil, le biais, la marge de masque et le contour du BER – et l’analyse de l’horloge transférée pour capturer avec précision le comportement de l’horloge asynchrone.

Parmi les autres fonctionnalités, on trouve la mesure de la fonction de transfert de tension (VTF) – le calcul précis d’une VTF, l’analyse du taux d’erreur binaire (BER) du système jusqu’à des niveaux de 1.e-27 ou 1.e-32, et la mesure de la hauteur et de la largeur du diagramme de l’œil, le biais, la marge de masque et le contour du BER – et l’analyse de l’horloge transférée pour capturer avec précision le comportement de l’horloge asynchrone.

« La capacité de valider nos solutions chiplets est cruciale pour assurer un avenir à la conception de puces hétérogènes, car cela garantit un fonctionnement transparent et une interopérabilité pour les solutions 2,5D/3D disponibles pour nos clients. Chiplet PHY Designer offre aux concepteurs un moyen rapide et facile d’extraire la conformité électrique de leurs solutions par rapport à la dernière révision de la spécification », explique Adrien Auge, Senior Staff Applications Engineer chez Alphawave Semi.