Le CEA-Leti collabore avec Intel dans le packaging 3D

Le CEA-Leti annonce une nouvelle collaboration avec Intel qui portera sur l’intégration 3D et le packaging des processeurs afin d’améliorer la conception des puces.

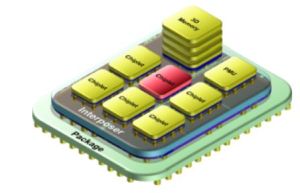

La recherche sera axée sur l’assemblage de chiplets plus petits, l’optimisation des technologies d’interconnexion entre les différents éléments des microprocesseurs, et sur de nouvelles technologies de collage et d’empilement des circuits intégrés en 3D, notamment pour la réalisation d’applications de calcul haute performance (HPC).

La technologie 3D, qui permet d’empiler les puces verticalement dans un dispositif, non seulement optimise la puissance des puces avec des interconnexions de packaging avancées entre les composants, mais cela permet également la création de chiplets à intégration hétérogène. Cela permet à terme de fabriquer des microprocesseurs plus efficaces, plus fins et plus légers. En outre, en mettant en œuvre de multiples solutions hétérogènes dans un seul packaging, les fabricants de puces bénéficient d’une flexibilité considérable en mélangeant différents blocs technologiques avec une IP différente et l’intégration de la mémoire et des technologies d’entrée/sortie au sein d’un même composant. Cela permet aux fabricants de puces de continuer à innover et à s’adapter aux besoins de leurs clients et partenaires.

La technologie 3D, qui permet d’empiler les puces verticalement dans un dispositif, non seulement optimise la puissance des puces avec des interconnexions de packaging avancées entre les composants, mais cela permet également la création de chiplets à intégration hétérogène. Cela permet à terme de fabriquer des microprocesseurs plus efficaces, plus fins et plus légers. En outre, en mettant en œuvre de multiples solutions hétérogènes dans un seul packaging, les fabricants de puces bénéficient d’une flexibilité considérable en mélangeant différents blocs technologiques avec une IP différente et l’intégration de la mémoire et des technologies d’entrée/sortie au sein d’un même composant. Cela permet aux fabricants de puces de continuer à innover et à s’adapter aux besoins de leurs clients et partenaires.

En 2019, Intel a présenté une nouvelle technologie d’intégration 3D, qui a adapté ces caractéristiques de conception. Cette technologie de packaging avancée, lancée dans les processeurs Intel Core avec technologie hybride Intel (nom de code Lakefield) se présente sous la forme d’un tout petit package physique pour une taille de carte électronique considérablement réduite afin d’offrir un équilibre optimal entre performances et efficacité énergétique.

En 2019, Intel a présenté une nouvelle technologie d’intégration 3D, qui a adapté ces caractéristiques de conception. Cette technologie de packaging avancée, lancée dans les processeurs Intel Core avec technologie hybride Intel (nom de code Lakefield) se présente sous la forme d’un tout petit package physique pour une taille de carte électronique considérablement réduite afin d’offrir un équilibre optimal entre performances et efficacité énergétique.

En juin 2020, le CEA-Leti a reçu le prix du meilleur article lors de la dernière conférence de l’IEEE ECTC pour ses travaux, réalisés dans le cadre de l’IRT Nanoelec, sur l’interposeur actif en silicium comme solution prometteuse vers l’intégration hétérogène 3D. Ces résultats ouvrent la voie aux futurs systèmes à haut rendement pour le calcul haute performance.